Critical Considerations: Designing Hardware for Optimum RF Performance at 18GHz

22/09/2025

With the likes of AMD’s Versal RF adaptive system-on-chip series pushing the boundaries of signal processing power and high-speed interfaces, focusing on how to optimise designs for RF performance at the higher frequencies of up to 18 GHz is becoming more important than ever.

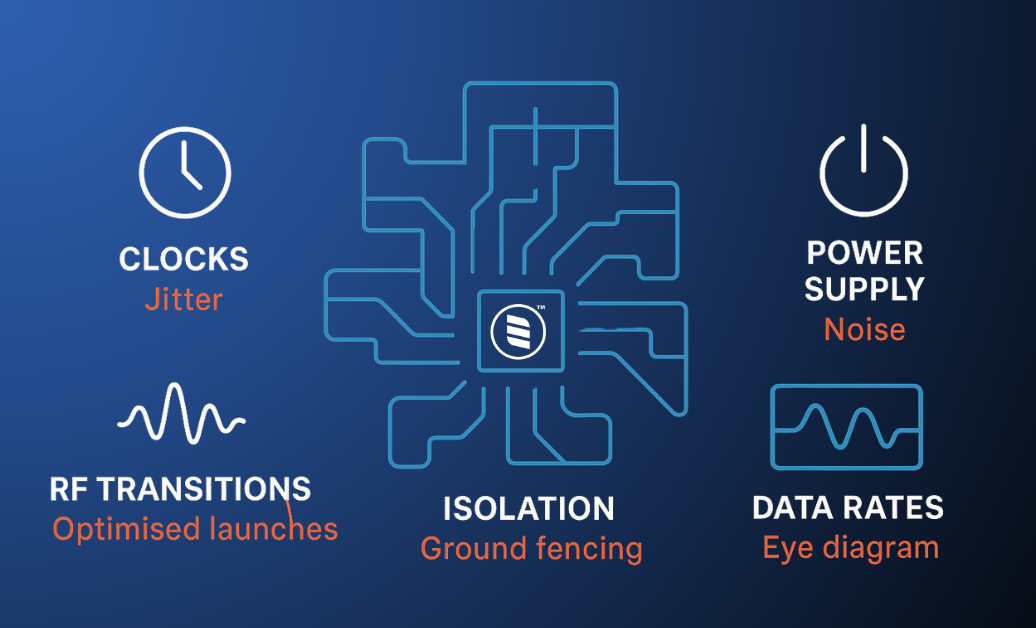

Slipstream Design’s expert Digital & RF engineering team specialises in tackling key challenges with Direct RF designs such as clock jitter, power supply noise, and signal integrity.

Direct RF refers to the ability to sample RF signals directly at their carrier frequency, eliminating the need for multiple frequency conversion stages. By moving analog-to-digital conversion closer to the antenna, Direct RF architectures reduce system complexity, lower latency, and open up wider instantaneous bandwidths for advanced signal processing.

Focusing on precision clock architecture, power integrity strategies, and RF isolation techniques ensures your high-power, high-frequency RF designs achieve reliable, high-performance operation in even the most demanding applications.Read on to discover how we’re ready to help.

Clocks

The Problem:

Direct sampling at RF frequencies up to 18 GHz typically (Nyquist zone dependent) requires sample clock rates above 18 GHz. This makes the jitter and phase noise quality of the sample clocking scheme critical.

Even small amounts of low frequency leakage into the high frequency sample clocks can have a dramatic impact on phase noise and hence system level performance. This is a particular problem when high speed digital and sensitive analogue domains are in close proximity.

Slipstream Design’s Approach:

We architect clocking with care, employing isolation strategies and implement layouts that are optimised for low leakage performance to reduce and improve phase noise and jitter performance. Our engineers apply proven techniques to physically and electronically separate clock sources from critical RF paths, ensuring signal integrity is maintained.

Power Supply Noise

The Problem:

Noise from switching regulators, digital circuits, and poor layout can couple into RF and analogue domains, compromising Power Supply Rejection Ratio (PSRR) and introducing spurious tones.

Slipstream Design’s Approach:

We use a holistic power integrity strategy, combining segmented power planes, careful return path management, and low-inductance decoupling. Our team evaluates PSRR performance early in the design process and uses filtering and isolation techniques to keep sensitive RF blocks immune to power supply fluctuations.

RF Connections / Transitions

The Problem:

Impedance mismatch in PCB traces, via transitions, or connector launches can result in degraded return loss and signal integrity. This is particularly problematic at higher frequencies such as 18 GHz.

Slipstream Design’s Approach:

We model all high-frequency transitions using 3D Electromagnetic (EM) simulation tools, ensuring that stubs, launch geometry, and interconnects are optimised with great care. Our layouts balance manufacturability and performance, with expertise in selecting the right transmission line format (microstrip, coplanar waveguide (CPW), or stripline) and isolation methods for each application.

RF Isolation

The Problem:

Poor RF isolation can lead to crosstalk, unintended coupling between subsystems, poor small signal gain responses and degraded spurious-free dynamic range (SFDR), particularly in mixed-signal and dense layouts.

Slipstream Design’s Approach:

We implement robust isolation techniques including ground fencing vias, component shielding, internal walls, PCB slotting, and multi-layer segregation of RF, digital, and power domains. We use carefully designed internal shielding structures when necessary, ensuring reliable performance in compact, high-frequency systems.

Data Rates

The Problem:

At high data rates, reflections, and skin-effect losses can cause eye closure and timing errors, affecting overall link reliability. Eye closure refers to the shrinking of the operating envelope in an eye diagram, which reduces voltage and timing margins, making it harder for digital receivers to distinguish between 0s and 1s.

Slipstream Design’s Approach:

We model high-speed paths with attention to trace length, impedance control, and signal rise times. Eye diagram and Time Domain Reflectometry (TDR) simulations are standard practice in our workflow, ensuring data interfaces (SerDes, JESD204B/C, high-speed ADC/DAC) meet timing margins and signal integrity targets without the need for excessive post-layout rework.

Conclusion

Direct RF can simplify hardware, boost flexibility, and enable true software-defined, multi-mission radios — at the cost of demanding ADC/DAC + DSP technology.

If you’re thinking about how Direct RF technologies such as AMD’s Versal RF Series may gain you an advantage over your competitors, our expert RF engineering approach guarantees reliable, high-quality RF and mixed-signal systems with superior signal integrity and reduced noise.

Talk to us today about your high-frequency RF design needs: info@slipstream-design.co.uk